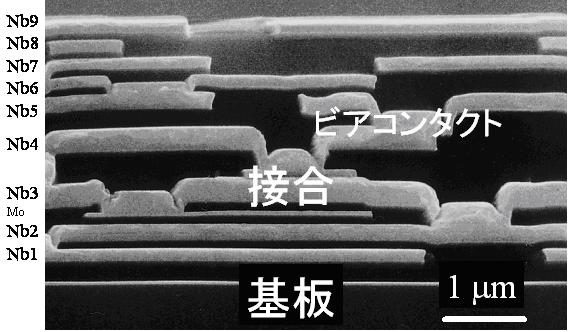

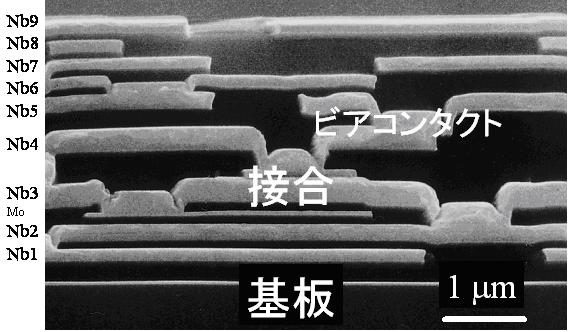

図1 今回開発した製造プロセスで試作したNb系超電導集積回路の断面SEM像

高度情報化時代の進展に伴い、大量の情報を高速に処理することへの需要が年々高まっている。この需要に応えるには、より速いクロックレートで動作するLSIが必要となる。しかし、微細化によるスケーリング則に従って進展してきた半導体LSIのクロックレートは、消費電力等の問題で限界を迎えつつあり、この限界を打破するには半導体CMOSと異なる原理で動作する素子が必要である。

超電導体を用い、半導体素子と異なる原理で動作する単一磁束量子(Single Flux Quantum : SFQ)素子は、最先端の微細化技術なしに100 GHz以上の超高速動作が可能であり、またゲートあたり1 W以下の低消費電力を実現できる可能性をも合わせ持つ。SFQ素子は複雑な処理をおこなうLSIを実現し得ることが実証されている半導体以外での唯一の素子でもある。このため、SFQ集積回路は半導体の限界を超えた高いクロックレートで動作するLSIを実現する第一の候補として期待されている。

情報通信基盤の重要な構成要素としてルータが挙げられる。将来、LSIの情報処理能力上足や発熱に起因する実装の制約から、ネットワークの停滞などが危惧されている。超電導工学研究所は、産学官共同プロジェクトに参加して超電導LSIの製造プロセス・回路設計・実装等の技術開発に取り組み、超高速ルータを実現するための超電導ネットワークスイッチの開発を目指している。

今回開発された超電導LSI製造プロセス技術は既存のNEC標準プロセスをもとに開発され、より高積層・高集積・高速動作を目指している。新プロセスは、最大9層のNb層を積層することが可能であり、磁場シールド層や配線層の設置が容易になっている。この高積層構造を実現するために、新プロセスは機械研摩による平坦化工程を含んでいる。また、ジョセフソン接合の臨界電流密度を従来の4倊の10 kA/cm2に高め、素子動作の高速化を図っている。その一方で、10万素子規模のLSIを想定しているので、接合特性のばらつきは1= 2%以下に抑えている。集積度の向上にも取り組んでおり、例えば最小接合の面積は従来の1/4の1.0 m2に縮小している。また、従来プロセスでは採用しなかった垂直積層型のビアコンタクトや、接合とシャント抵抗層との直接コンタクト構造なども新プロセスで採用した。開発を担当した同所プロセスグループには最先端の半導体プロセス開発に従事した経験を持つ研究者も参加しており、超電導回路プロセス研究者と共同で、ジョセフソン接合をはじめ、Mo抵抗膜、ビアコンタクト、層間絶縁層等のさまざまな回路要素の信頼性向上、また成膜・エッチング・洗浄等の各プロセスの信頼性向上に取り組んでいる。

本製造プロセスを用いた集積回路の試作・評価も進んでいる。すでに吊古屋大学が同所と共同で、本プロセスを一部用いて作製したSFQシフトレジスタ回路を120 GHzで動作させることに成功している(Supercom Vol.14, No.5, 2005.10)。同所プロセス開発グループの一員である佐藤哲朗主管研究員は「今後は回路動作実証を通じて、この新しいプロセスの優位性実証や信頼性向上に取り組んでいきたい《と語っている。

(KHT)