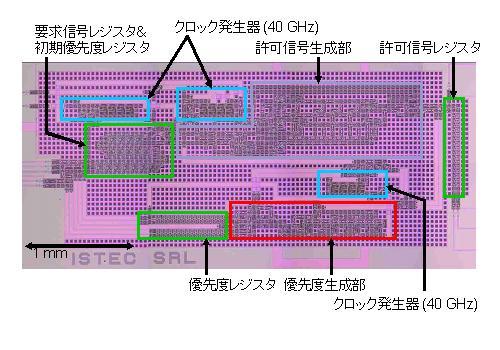

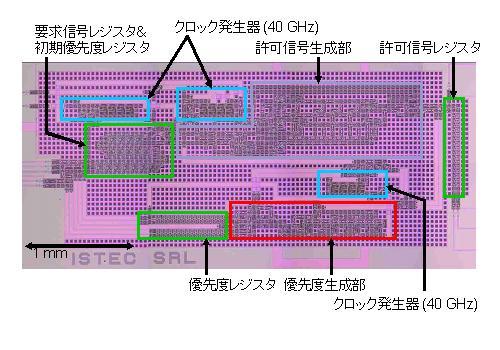

図1 SFQスケジューラ回路 4×4クロスバースイッチ対応、消費電力:920 μW、ジョセフソン接合数:3071

SFQ回路は半導体回路と異なり、量子化された磁束の有無で情報の‘1’、‘0’を表現する。1ビットを表現する磁束は数ピコ秒幅・数百マイクロボルトの微小電圧パルス信号として回路中を伝搬する。そのため、半導体回路に比べて高速であり、しかも消費電力が少ないという特長を持つ。

インターネットの普及に伴い、今後ますます大容量通信を支える基盤技術が必要になる。そこで、超電導工学研究所では、SFQ回路の超高速・低消費電力特性を活かしたSFQハイエンドルータの研究を行っている。ハイエンドルータは、データ経路であるデータパスと、データパスで衝突が起きないようにデータ入力を調停するスケジューラに分けられる。特に、スケジューラは、すべてのデータの行き先を見比べてデータパスでの衝突可能性を調べるため、並列化による高速化が困難である。ハイエンドルータの高速化に伴い、スケジューラが律速となり半導体ルータの高速・大容量化を妨げる一つの要因となっている。

今回開発されたSFQスケジューラ(図1)は、ゲートレベルパイプライン化などのSFQ回路独自の高速回路設計技術を応用したもので、従来のスケジューリングアルゴリズムを変えることなく半導体スケジューラより約100倊速い40 GHzクロックで動作することを実証した。発表されたSFQスケジューラは4入力・4出力スイッチ対応であるが、クロック速度の低下なしに拡張可能な回路構成をとっている。回路設計には超電導工学研究所が情報通信研究機構・吊古屋大学・横浜国立大学と共同で研究・開発したSFQ標準セルライブラリCONNECTとセルベース設計技術を用いている。SFQスケジューラは約3000接合で構成される。また、回路ブロック間を受動配線で接続し、速度向上を図っている。本研究は、低消費電力型超電導ネットワークデバイスの開発の研究として、新エネルギー・産業技術総合開発機構の委託により実施したものである。

実際にSFQスケジューラの設計とテストを行った亀田義男主任研究員は「これまでに蓄積してきたSFQ回路設計技術・作製プロセス技術により、複雑な機能でありながら40 GHzクロックで動作するスケジューラの実証ができた。今後、スケジューラとデータパスを統合した回路設計を進める。《と述べている。

(輪)