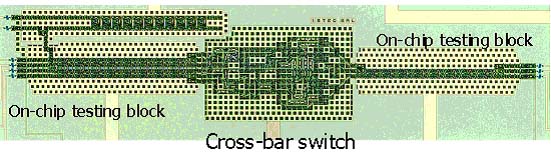

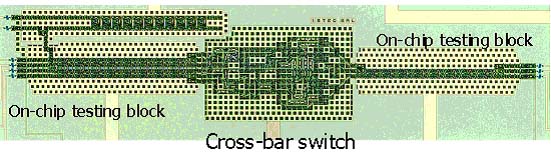

図1 2x2クロスバースイッチ

SRL低温デバイス開発室では、SFQ回路技術を用いてパケットスイッチを実現する研究をおこなっている。SRL低温デバイス開発室の萬伸一主任研究員によれば、グループではパケットスイッチ回路を40GHz以上のクロック速度で動作させることを目的としているということである。回路がパケットの伝送スピードと同等かそれ以上の速度で動作できるので、並列化処理を抑え、制御処理の単純化、回路規模の低減が可能である。これが実装負担をも軽くし実効的に性能向上に結びつく。現在の電子ルータが抱えている諸問題を一気に解決する技術とみて精力的に研究開発を続けている。

SRL低温デバイス開発室では、第一段階として、基幹要素回路である二つのパケットの進行方向を切り替える2x2クロスバースイッチ回路のデモンストレーションを試みた。2x2クロスバースイッチは論理回路であり論理設計ができる環境が必要である。その上高速動作を目指すためにはピコ秒レベルの精密なタイミング設計も必須である。SRL低温デバイス開発室ではトップダウンセルベース設計環境を構築、そのもとで設計を行った。セルライブラリは吊古屋大、横浜国大、通信総合研究所、NEC基礎研究所と産官学共同で開発されたCONNECTを用いている。図1に作製された回路を示す。回路は、スイッチ回路ブロックとオンチップ動作試験用の回路ブロックからなる。このオンチップテスト回路は吊古屋大学で開発されたものでCONNECTセルライブラリに搭載されている。動作実験の結果50GHzまでの安定な動作を確認した。実際に設計と動作実験をおこなった亀田義男主任研究員によると、実は設計は40GHzをターゲットになされたのだという。ピコ秒レベルの精細なタイミング解析のもとでのタイミング設計が動作マージンを広め50GHzまでの動作を可能にしたと言う。強固な産官学連携のもとで構築されたセルライブラリの信頼性と高度な設計手法の確立が検証された。

SRL低温デバイス開発室では今後さらにスイッチ回路規模を拡大し実用化を目指すという。そのキーテクノロジとして、萬主任研究員は二つの技術をあげた。ひとつは回路の自動配置配線をおこなうツール開発、もうひとつは回路間の配線を現在のジョセフソン線路(JTL)からマイクロストリップ線路もしくはストリップ線路(PTL配線)に置き換える技術である。自動配置配線技術について亀田主任研究員は、既に数万接合級の回路の論理セル配置にはめどがたっているとしている。PTL配線技術を研究している橋本義仁主任研究員は、この技術は回路のタイミング設計がより容易になるうえ、現在の回路規模・消費電力を最大80から90%縮小し、動作遅延を著しく小さくすることができるなど、大きなイノベーションがSFQ回路技術にもたらされる。既にLSI中の複数の中規模回路ブロックの間を結ぶ配線技術は実用レベルにあるとのことである。このような技術の組み合わせにより、従来は非常に困難と見られていたSFQ回路規模拡大がスケーラブルにできる。実用的なSFQLSIの実現に大きく近づいた。今後の研究の進捗が期待される。

(まんぼう)