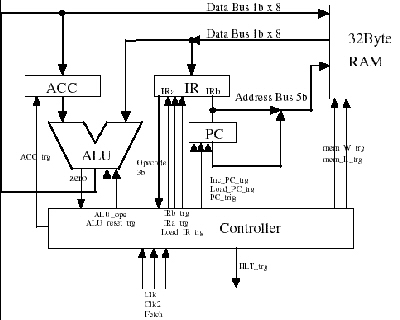

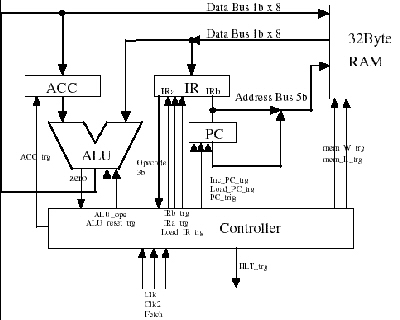

図1 SFQマイクロプロセッサのブロック図

図2 SFQマイクロプロセッサのチップレイアウト

図3 ALUの測定結果。図はAND operationの例を示す。

横浜国大では、これまで大規模SFQ集積回路の設計技術の確立を目指して、TIPPY(Tiny Processor Project of Yokohama)と呼ばれる小規模SFQマイクロプロセッサの開発プロジェクトを行っていた。今回設計したTIPPY2は、図1に示すように2つのレジスタ(ACC, IR)と、1ビットALU、プログラムカウンタ(PC)、コントローラ(Controller)から成る。命令数は6個と少ないが、プロセッサの動作に欠かせない、判定や分岐の機能を持つという。回路はBDD SFQ ゲート(BDD: Binary Decision Diagram) と呼ばれるデュアルレールの非同期式ゲートで構成されているため、タイミング設計が容易であり、またゲート数も少なくてすむという。また、SFQ回路の高速性をもっとも効率良く引き出すため、ALUでのデータ処理は、全てシリアルデータ単位で行われる。シリアルデータ処理によりシステムサイクルは悪くなるが、ハードウェアを大幅に簡略化できるという利点がある。更に、回路のクロッキングのために、各レジスタにローカルクロックジェネレータを配置した分散型クロックアーキテクチャという新しい考え方を用いている。図2にはHypres社の標準Nbプロセスを用いて設計したマイクロプロセッサのレイアウトを示す。設計には横浜国大が開発したBDD SFQセルライブラリが用いられている。チップ寸法は10mm ×10mm、接合数は5118JJであった。回路の全ての正常動作が論理シミュレーションにより確認され、動作周波数の上限は6.25GHzであった。吉川助教授によれば「今回の設計では最大周波数を狙っていないが、NEC社のNbプロセスを用いれば、25GHzの動作が可能《であるという。

一方、ALUの動作の低速試験も行われ、その正常動作が確認された。図3にはALUのAND動作の実験結果を示す。回路全体のDCバイアスマージンは±3.3%であったという。ALUは730JJで構成され、寸法は2300mm×1300mmであった。

吉川助教授によれば、「セルベース設計法の確立と、論理シミュレーションツールを含むトップダウン設計環境の整備により、この数年でSFQ集積回路設計技術は飛躍的に進歩したと思う。今では、クロック周波数が10~20GHzで動作する1万JJ規模のSFQ集積回路が容易に設計できるようになった。また、同様の技術を用いて千JJ規模の回路動作の実証例がいろいろな研究機関で出始めている。今回のTYPPYプロジェクトの成果は、これらのSFQ設計技術の有効性を示すばかりでなく、ビットシリアルアーキテクチャや非同期回路方式など、SFQ回路に適した新規アーキテクチャの提案とその実証という意味で、今後の大規模SFQ集積回路開発に与える影響は大きいと思う。《と述べている。また、同助教授は「我々は既に、吊古屋大、北大と共同で、COREと呼ばれるSFQマイクロプロセッサの次期開発プロジェクトをスタートしている。COREプロジェクトにより今年度中に世界最大規模の1万JJを含むSFQマイクロプロセッサの動作を実証する予定である。いまのところ、COREプロジェクトの障害になるような技術的な障害は何も見あたらないと思う。《と強気の意見を述べている。

図2 SFQマイクロプロセッサのチップレイアウト

図3 ALUの測定結果。図はAND operationの例を示す。

(のんだくれ)