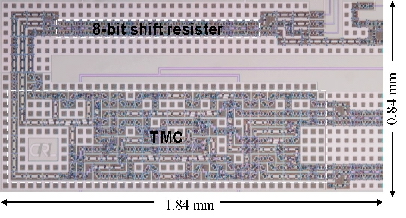

図1 TMC回路の顕微鏡写真

図2 TMC高速動作試験回路のブロック図

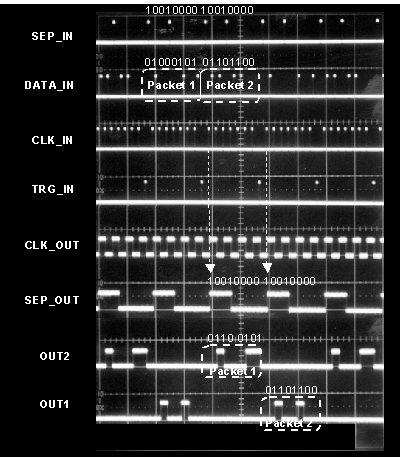

図3 TMC回路の高速動作試験結果

動作に成功した回路は、トランスミッション・チェッカー(TMC)と呼ばれる回路で、タンデム・バンヤン型ネットワークスイッチのキーコンポーネントの1つということである。タンデム・バンヤン・スイッチは、バンヤン・ネットワークを直列に接続した構成で、出力にバッファーを配置するという特色を持つ。この構成を採用することで、現在主流である入力バッファー型のスイッチに比べて、比較的少ないハードウェア量で高スループットを得ることが可能となる。また、スイッチの構成要素がバンヤン・ネットワークの構成要素である2×2スイッチ、TMC、出力バッファーの3つとシンプルで、パケットがスイッチの入口から出口までほぼクロックと同一方向に移動するためタイミング設計が容易で、超高速なSFQ回路の動作に適したスイッチ構成となっている。

今回動作したTMC回路は22個の論理ゲートからなり、CRLとNEC基礎研究所、吊古屋大学、横浜国立大学が、NEC Nb標準プロセス用に開発したSFQセルライブラリ(CONNECTセルライブラリ)を使用して設計レイアウトされたという。図1は試作されたTMC回路の顕微鏡写真である。TMC回路はバンヤン・ネットワークから出力されるパケットのうち、データを保有しかつ正しいアドレスに転送されたことを示す「11《というフラグと、データを保有するものの間違ったアドレスに転送されたことを示す「10《のフラグを検出しルーティングを行う。「11《のフラグを検出した場合、パケットを出力バケットを出力バッファーに転送し、「10《のフラグを検出するとそれを「11《に書き換えて再びパケットをバンヤン・ネットワークに転送する。設計において重要となる各ゲートの入力タイミングは、CONNECTセルライブラリに含まれるタイミング情報をもとに、ハードウェア記述言語を使用した論理シミュレータを利用して行われている。

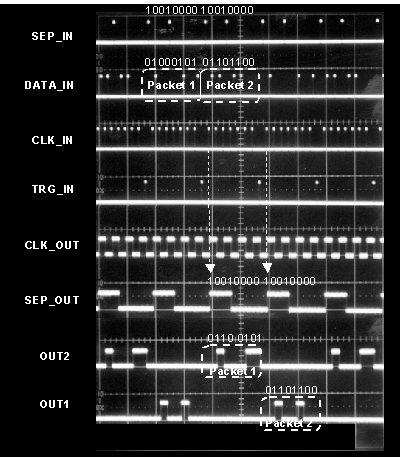

40GHzでの動作実証はオンチップテスト法を用いて行われた。図2は高速試験回路のブロック図を示している。回路規模はジョセフソン接合数で1545個(TMC回路は接合数611個)ということである。入力信号は、パケット本体であるDATA信号、パケット及びパケット内の転送情報ビットとデータビットを分離するSEP信号、高速クロックを発生させるTRG信号、そしてCLK信号である。実験は被試験回路であるTMC回路の入力側に接続されたシフトレジスタに低速でデータを書き込み、オンチップに搭載したクロック発生回路からの高速クロック信号によりデータを出力側のシフトレジスタに転送し、それを再び低速で読み出すという手順で行われた。

図3はTMC回路の27GHzでの動作試験結果である。入力側の8ビットシフトレジスタに書き込まれたDATAパケット「01100101《が、TRGパルスにより発生した13ビットの高速クロックパルスによりOUT2(出力バッファーへの出力)へ正しく転送されている。一方、DATAパケット「01001100《は、転送情報ビット「10《を「11《に書き換えられてOUT1(バンヤン・ネットワークへの出力)へ正しく転送されている。動作バイアスマージンは27GHzで±6%、40GHzでは±1.7%まで低下するものの正常な動作が確認されている。

この回路の開発に当たった寺井主任研究官(CRL関西先端研究センター)は「SFQセル単体、あるいはDEMUX、シフトレジスタなど規則性を持った回路が40GHz以上で動作したという報告はこれまでにもあったが、今回の結果は複数の多様な論理ゲートを組み合わせた600個以上のジョセフソン接合を含む回路が40GHzという高速で動作したという点で意義がある。この成果は、CONNECTセルライブラリの開発グループが目指しているセル設計手法が、高速で動作する大規模SFQ回路を実現する上で極めて有効であることを示している。《と語っている。

図2 TMC高速動作試験回路のブロック図

図3 TMC回路の高速動作試験結果

(関西人)