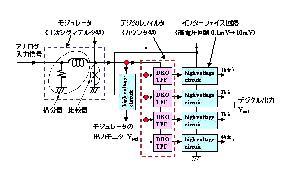

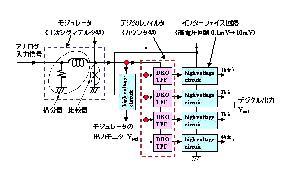

図1 今回試作測定したΣ-Δ型超電導AD変換器の構成

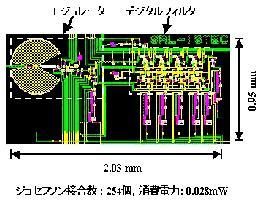

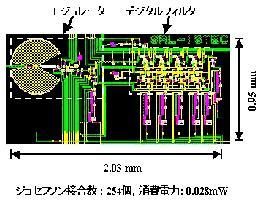

図2 今回試作測定したΣ-Δ型超電導AD変換器の回路パターン

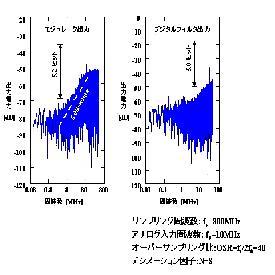

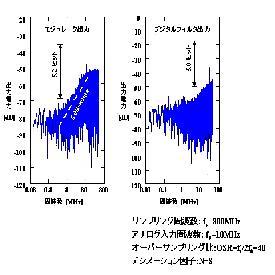

図3 測定結果(ノイズシェーピング特性)

左図:モジュレータの出力信号の周波数パワースペクトル

右図:AD変換器の出力信号の周波数パワースペクトル

この成果は、1998年度より、ISTECが、NEDOより委託を受けて実施している「超電導応用基盤技術研究開発プロジェクト」の一環として超電導工学研究所が行っている超電導回路設計製作と特性測定の研究開発の中で得られた。

試作した超電導ADコンバータは、シグマーデルタ(Σ-Δ)型と呼ばれるタイプで、回路的には、モジュレータ(AD変換回路)とデジタルフィルタ(デシメーションフィルタ)とインターフェース回路(高電圧回路)とから成り立っている。今回は、これらを一体化してひとつの基板上に製作し、デジタル測定により、ADコンバータとして正常に機能していることを確認した。これまでにも、モジュレータのみやデジタルフィルタを単独で超電導回路で製作して動作させた報告例はあったが、今回は、初めてこれらを一体型の回路として作成し動作確認に成功したものである。

図1は、設計・試作した超電導AD変換器の回路構成である。モジュレータは、Σ-Δ型モジュレータの基本形である1次(伝達関数が1次)のローパス型であり、アナログ入力信号を1ビットのデジタル信号列に変換する。このとき、デジタル信号のパルス密度が入力信号の振幅に対応して出力される。デジタルフィルタは、伝達関数の次数が1次で、デシメーション因子 8の(すなわち1/8にデータレートが下げられる)デシメーションフィルタであり、モジュレータからのデジタル信号列を平均化処理して、量子化ノイズ(モジュレータでアナログ信号をデジタル化するときに量子化ノイズとよばれる雑音が生じる)を除去し、高精度の信号をとりだす。またインターフェイス回路は、低温のSFQ回路から出力される微小振幅の超高速パルス信号を室温の半導体回路で取り扱える振幅・ビット速度の信号に変換する回路である。ADコンバータとしての出力はデジタルフィルタの出力(4本:4ビット幅)としてチップ外に取り出される。またモジュレータ単独での動作を確認するために、モジュレータの出力信号を分岐してチップ外に取り出せる様になっている。

図2は、設計・試作した超電導ADコンバータの回路パターンである。使用したジョセフソン接合はAlOxバリヤのNb接合である。この回路には254個のジョセフソン接合が含まれている。消費電力は0.028mW、回路のサイズは2.03mm x 0.95mmである。なお試作チップの製作は、NEC基礎研に依頼され、Nb接合標準プロセス試作ライン(ジョセフソン電流密度2.5KA/cm2)で製作されている。

図3は測定結果である。この測定には、当研究所で独自に開発した高速高感度のデジタル計測システムを用いている。このシステムでは、ADコンバータからのデジタル出力をシリアルパラレル変換してビット速度を下げてから半導体メモリに一旦記憶させ、あとでオフラインで高速フーリエ変換(FFT)処理をして、特性(周波数スペクトル)を得ている。Σ−Δ型ADコンバータの場合、アナログ測定では特性を定量的に把握することがむずかしいため、このようなデジタル測定をおこない、ADコンバータの出力特性を正確に理論値と比較できるようにしている。

図3左側はモジュレータの出力特性(周波数スペクトル)である。周波数10MHzのところにアナログ入力信号に対応する電力ピークが観測され、モジュレータの動作周波数800MHzの半分(400MHz)までノイズ電力が観測され、Σ−Δ型の特徴である高周波側に多くのノイズが偏在する(ノイズシェーピングとよばれる)特性が現れている。この図からダイナミックレンジ(信号とノイズの比)は33dBある。これはADコンバータの変換ビット精度にすると5.2 ビットに相当する。測定されたノイズシェーピングの傾きは6dB/オクターブであり、理論値とよく一致している。

また図3右側は、デジタルフィルタの出力特性であり、これがADコンバータの正規の出力特性である。この場合も周波数10MHzのところに信号電力のピークが観測されている。また、量子化ノイズは、デシメーションフィルタを通すことによって、フィルタのデシメーション周波数(100MHz)の1/2の50MHz以上が除去されている。ここでのダイナミックレンジは32dB(5.0ビット)である。今回の測定は、サンプリング周波数(モジュレータの動作周波数)800MHzでおこなったが、これは測定治具の周波数帯域の上限を考慮したためで、回路シミュレーションでは、22GHzまで動作している。

この成果によって、SFQ回路で超電導ADコンバータが製作でき、理論どおりに動作することが初めて実証された。また測定法も確立されたので、今後の超電導ADコンバータの研究開発に拍車がかかるものと期待される。

この回路の設計と測定を担当する長谷川晴弘主任研究員は、「超電導工学研究所では、この超電導ADコンバータの応用ターゲットとして、第4世代移動体通信の基地局での採用が期待されているソフトウエア無線に必須とされる高速高精度のADコンバータを考えている。このためにはキャリヤ周波数2〜5GHz,周波数帯域100MHzのアナログ信号を、変換ビット精度12〜16ビットでデジタル化する必要があるといわれている。本成果はまだこのスペックを満たしていないが、シミュレーションでは、2次のモジュレータと3次のデシメーションフィルタの組み合わせで、サンプリング周波数を12GHz以上にすると、このスペックが満足されるという結果を得ている。今後このスペックの実現に向けて回路を高度化して行きたい」と語っている。

図2 今回試作測定したΣ-Δ型超電導AD変換器の回路パターン

図3 測定結果(ノイズシェーピング特性)

左図:モジュレータの出力信号の周波数パワースペクトル

右図:AD変換器の出力信号の周波数パワースペクトル

(しなの路)