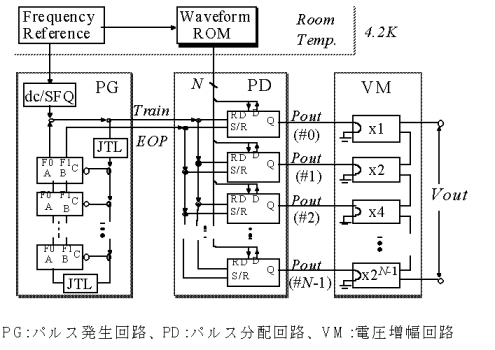

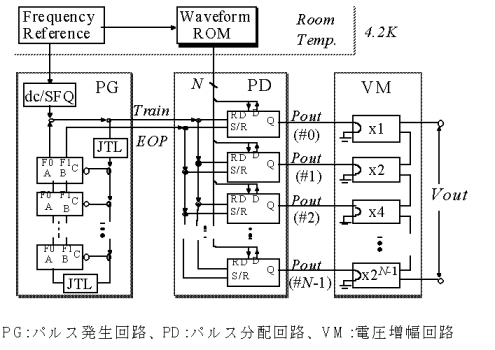

図 磁束量子を用いる高精度電圧標準の回路構成図

SFQを担体として利用することによって、極めて高速かつ低消費電力での論理演算やAD・DA変換が可能であることは、すでに、米国ニューヨーク州立大学のLikharev教授のグループらによって実証されているが、交流電圧標準の確立という具体的な目標をもった回路の試作は行われていない。電子技術総合研究所は国立の研究機関として電圧の国家標準を確立・維持する義務があり、これまでにNb系ジョセフソン素子を用いた直流電圧標準の確立・維持を行ってきた。今回のSFQ-DAコンバータの開発は、ジョセフソン素子を用いた電圧標準を交流(数kHz)にまで拡張することを目的として行われているものである。

同コンバータは、10 MHzの外部基準信号を基に、4.2 Kに冷却されたチップ上で10 GHzクロックのSFQパルスを発生する回路(『パルス発生回路』)、発生したSFQパルスを分配する回路(『パルス分配回路』)及びSFQパルスを入力線に与えることによって高精度電圧を発生する回路(『電圧増幅回路』)から構成される(図を参照)。これら3つの要素回路の内、『パルス発生回路』と『パルス分配回路』は、独自のアイデアに基づいて設計を行い、電子技術総合研究所内に整備されたジョセフソン接合集積回路作製ラインを用いて試作された。試作された回路の評価は、数100 Hzのデジタル信号をdc/SFQ変換回路を通して入力させ出力をSFQ/dc変換回路を通して読み出す方法によって行い、正常な動作が行われていることが確認された。『電圧増幅回路』についてはニューヨーク州立大学のPolonsky博士が考案した回路を採用することにしており、その基本動作については、米国Hypres社において作製されたチップによって、Polonsky博士らによりすでに確認が行われている。

最終的な開発目標としている12ビットのDAコンバータでは、『電圧増幅回路』は2048個のdc-SQUIDを含み必要なジョセフソン接合の数は1万個以上になる。そのような規模の集積度を有する超伝導デジタル回路はこれまでに作製された例がなく、極めてチャレンジングな目標であるといえる。今後のステップとしては、1999年度中に3つの要素回路を1チップ上に統合した4ビットDAコンバータを設計、試作し、その後、8-10ビットDAコンバータを経て、2001年度末までには12ビットDAコンバータを開発する予定である。

なお、今回の「パルス発生回路」と「パルス分配回路」の試作・評価に関する研究成果は、9月14日から17日にスペイン、バルセロナ市において開催されるEUCAS'99において発表される。

(夢追い人)